CPU

# CPU

# 1. CPU的功能和基本结构

# 1.1 CPU的功能

指令控制

取指令、分析指令、执行指令、顺序控制

操作控制

产生操作信号,将信号送往部件并进行动作

时间控制

对各种操作加以时间上的控制

数据加工

中断处理

# 1.2 CPU的基本结构

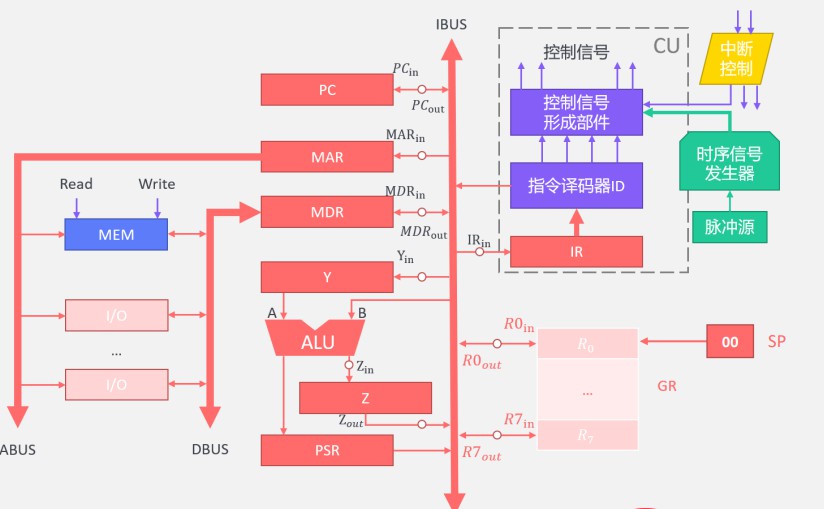

# 1.2.1 运算器的组成

接收并执行从控制器的命令;对数据加工和处理

1.算术逻辑单元:ALU

2.暂存寄存器:Y、Z

3.累加寄存器/累加器:ACC/AC

4.通用寄存器:GPR/GR

5.程序状态字寄存器:PSR/PSW

6.移位寄存器/移位器

7.计数寄存器/计数器

# 1.2.2 控制器的组成

指挥中枢,根据指令要求指挥全机协调工作

1.指令寄存器:IR

2.程序计数器:PC

3.指令译码器:ID

4.存储器地址寄存器:MAR

5.存储器数据寄存器:MDR(MBR)

6.时序系统:CLOCK

7.微操作信号发生器

# 1.2.3 寄存器的设置

1.指令寄存器:IR

2.程序计数器:PC

3.累加寄存器:ACC/AC 暂存寄存器:Y、Z 通用寄存器:GPR/GR

4.程序状态(字)寄存器:PSR/PSW

5.地址寄存器:MAR

6.数据缓冲寄存器:MDR(或MBR)

# 2. 指令的执行过程

# 2.1 指令周期

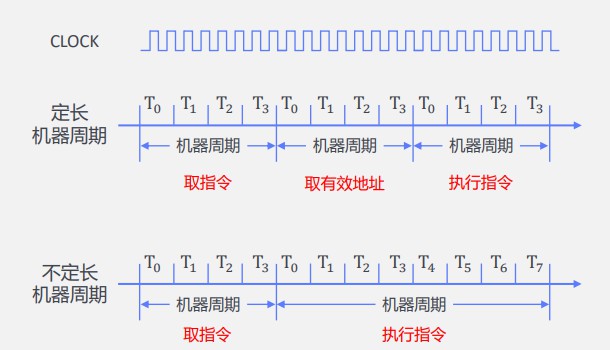

CPU从主存中取出并执行完成一条指令的时间

指令周期通常为若干机器周期

一个机器周期:若干时钟周期/节拍脉冲/T周期

# 2.2 四个阶段

取指周期:取指令

间址周期:取有效地址

执行周期:执行指令

中断周期:响应中断

# 2.3 指令执行中的数据流向

取指周期: (PC)->MAR->MEM->MDR->IR

间址周期: Ad(IR)->MAR->MEM->MDR

执行周期:无

中断周期: (SP)-1->SP->MAR (PC)->MDR->MEM 向量地址->PC

# 2.4 指令执行方式

顺序执行方式:各指令串行执行 控制简单;执行速度慢,机器效率低;

重叠执行方式:前一条完成之前开始后一条 指令的执行时间大大缩短了 硬件开销大(预读取部件),控制逻辑更加复杂

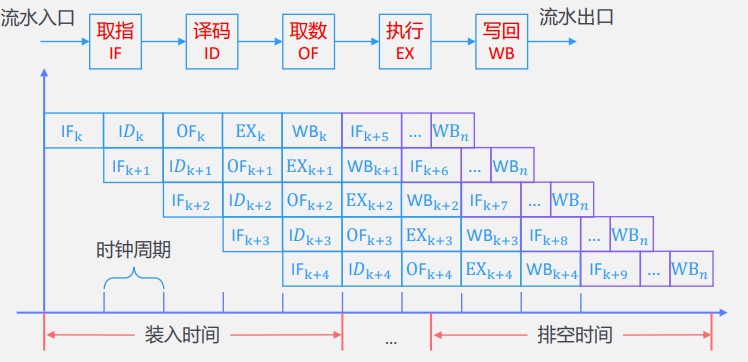

指令流水方案:把指令执行过程划分成若干复杂度相当, 耗时大致相等的子过程 每个子过程由一个独立的部件完成 流水线上各功能部件并行

流水线性能指标:吞吐率:单位时间内完成任务量 加速比:同一批任务不使用流水线与使用流水线时间比 效率:流水线上设备利用率