存储系统

# 存储系统

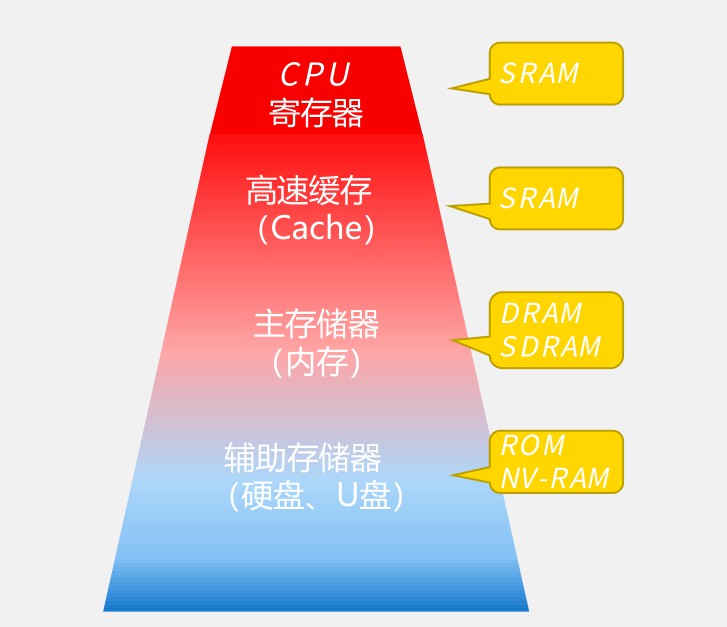

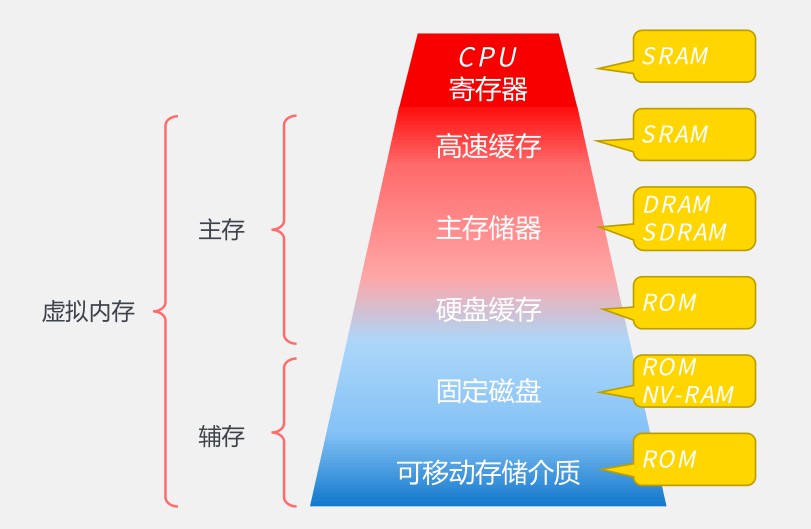

# 1. 存储器的层次结构

# 1.1 存储器的层次结构

高速缓冲存储器

Cache Memory(L 1 ~L 3 缓存)

主存储器

内存条

辅助存储器

固定磁盘(硬盘、磁盘、闪存) 可移动存储介质(U盘、光盘、磁带)

# 1.2 局部性原理

**虚拟内存:**从逻辑上扩充内存容量的存储器系统

局部性原理:

- 时间局部性

- 空间局部性

比如说CPU使用高速缓存中的数据,但是高速缓存中的数据来自主存存储器,那就会有个问题,主存储器中什么样的数据适合缓存到高速缓存中供CPU使用呢?答案可以从时间和空间上来找,第一:有一个变量经常用来做计算,不如求几个数的和,这就是时间局部性,第二:高速缓存中的数据使用完后,CPU大概率会执行这段数据在主存储器中的相邻下一个数据,这就是空间局部性。

# 2. 半导体存储器

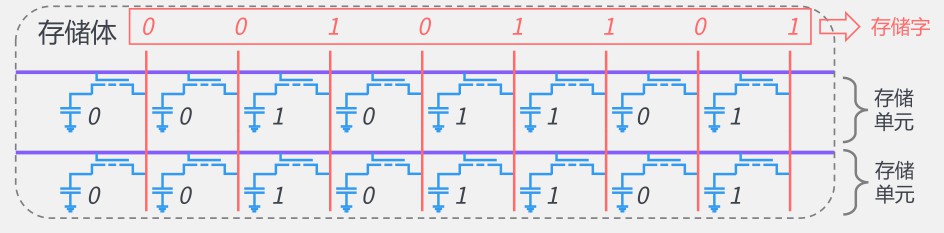

# 2.1 主存储器模型

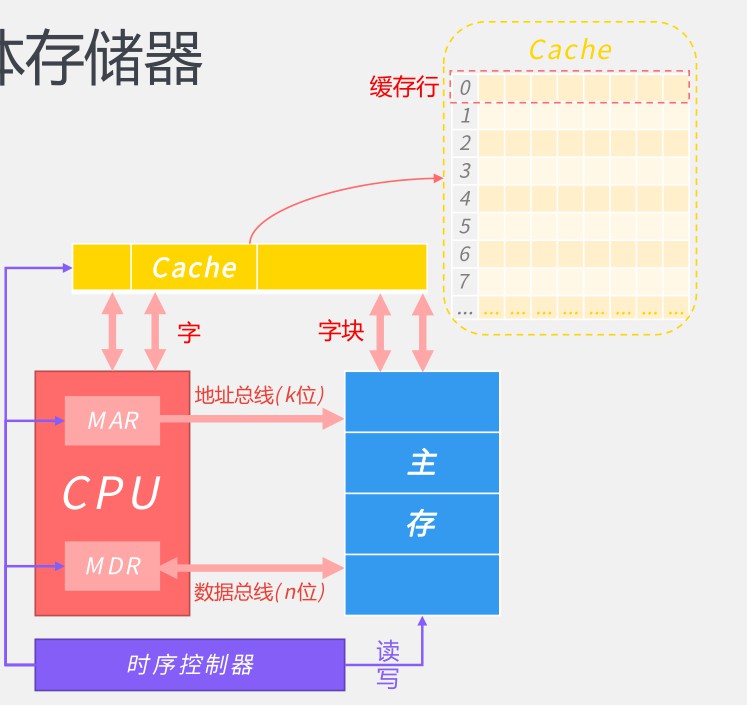

CPU与主存储器的连接

数据总线:

存取周期:两次连续存取的最小时间间隔

存储器总线宽度=数据总线位数=存储字长

数据传输率=存储器总线宽度/存取周期 单位时间内存取二进制信息的位数

地址总线:

存储容量:半导体存储芯片所能存储的二进制信息位数(单位bit) 可寻址最大范围:2 𝑘 × 𝑛(单位bit,1Byte=8bit) 1P = 1T × 2 10 = 1G × 2 20 = 1M × 2 30 = 1K × 2 40 = 1B × 2 50

# 2.2 半导体存储器

# 2.2.1 RAM(Random Access Memory)

- 随机存取存储器,可随机读写,断电易失

- 静态(static)RAM:

- 以触发器存储二进制位(6个MOS管)

- 动态(dynamic)RAM:

- 一个/三个MOS管和一个电容存储二进制位

- 刷新操作,给电容补电

- 非易失性(non-volatile)RAM:

- 采用CMOS管构成的低功耗SRAM存储单元

- 使用锂电池作为后备电源

# 2.2.2 SRAM与DRAM对比

静态(static)RAM:

- 以触发器存储二进制位(6个MOS管)

动态(dynamic)RAM:

- 一个/三个MOS管和一个电容存储二进制位

- 刷新操作,给电容补电

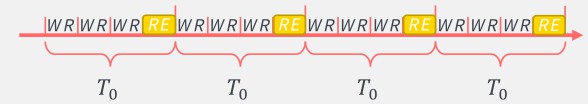

- 集中刷新:2ms内安排时间全部刷新

- 分散刷新:每次读完就刷新

- 异步刷新:每间隔一段时间刷新一行

# 2.3 ROM(Read-Only Memory)

只读存储器,可随机读,不可写入,非易失性 掩膜式只读存储器(MROM) 一次性可编程只读存储器(PROM) 可擦除可编程只读存储器(EPROM) 紫外线擦除(UV-EPROM) 修改次数有限,写入耗时 电擦除(EEPROM) 闪速存储器(Flash Memory) 固态硬盘(Solid State Drives)

# 3. 高速缓冲存储器Cache

# 3.1 基本概念

介于CPU和主存之间,缓解二者速度矛盾

局部性原理:时间/空间局部性 访问顺序:CPU->Cache->主存

Cache中存放主存 部分数据 的拷贝(副本)

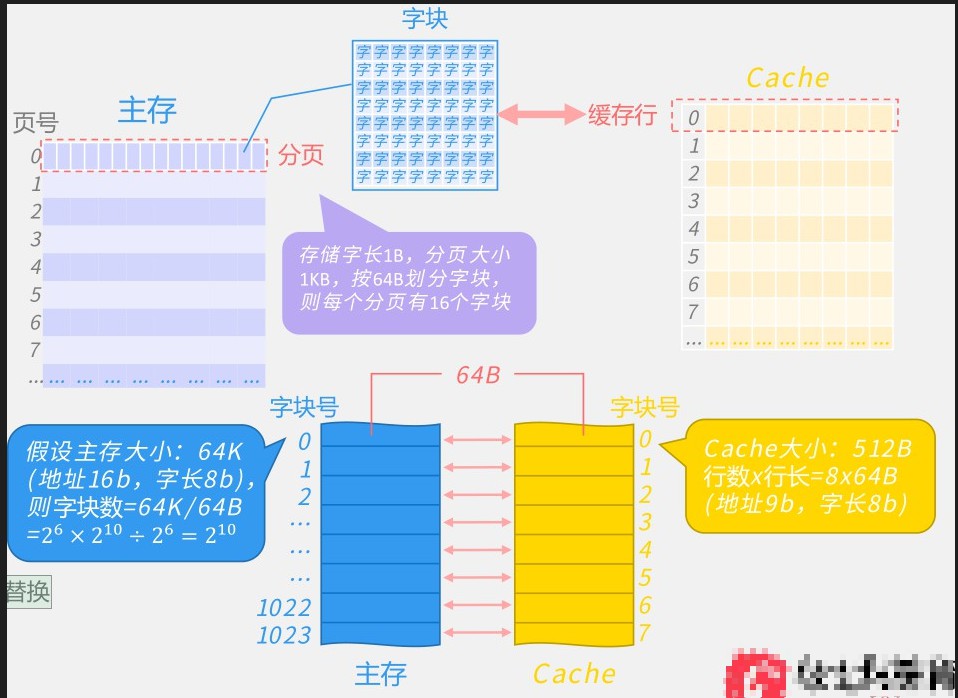

缓存行/缓存块:与主存传送数据的基本单位(Byte)

缓存命中率:85%+

- Cache大小

- Cache组织形式

- 程序特性

# 3.2 Cache的组织结构

Cache存储体

- 存放从主存调入的数据

- 由多个缓存行/字块构成:64B

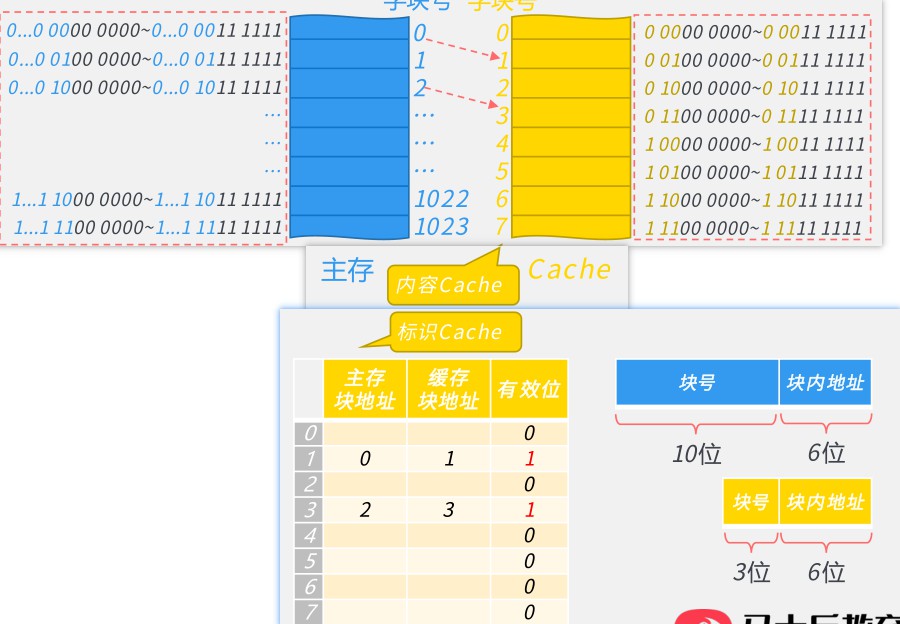

地址转换机构/部件

- 实现主存地址到缓存地址的转换

- 目录表,记录地址映像关系

替换机构/部件

- 按照一定策略(算法)进行数据块替换

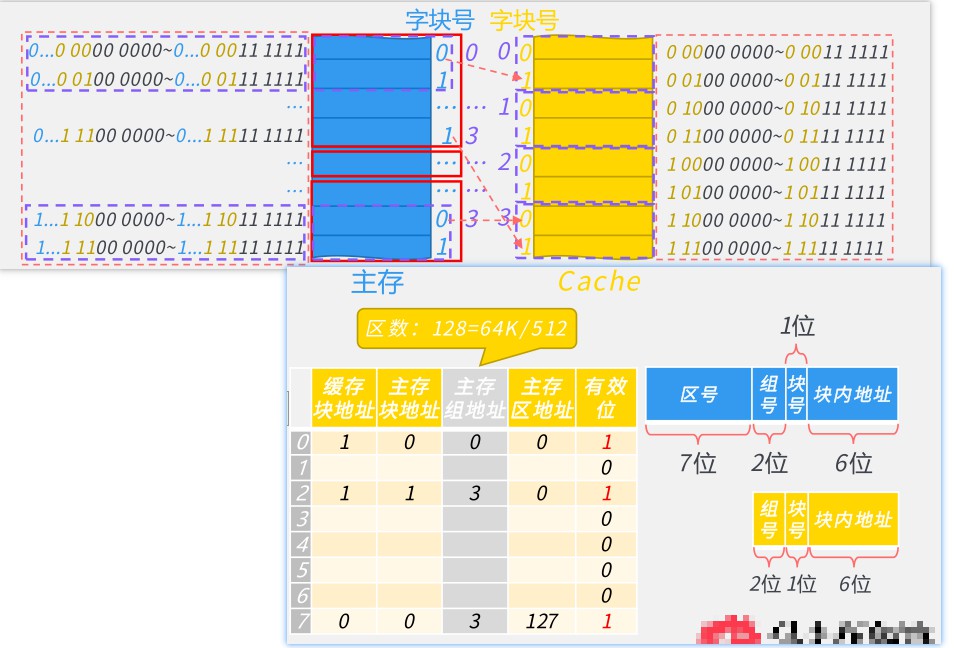

# 3.3 Cache与主存的映像

# 3.3.1 全相连映像(映射)

空位随意放

任意主存字块放到Cache任意位置

优点:命中率比较高,Cache存储空间利用率高

缺点:每次访问都要与全部内容比较,速度低,成本高,应用少

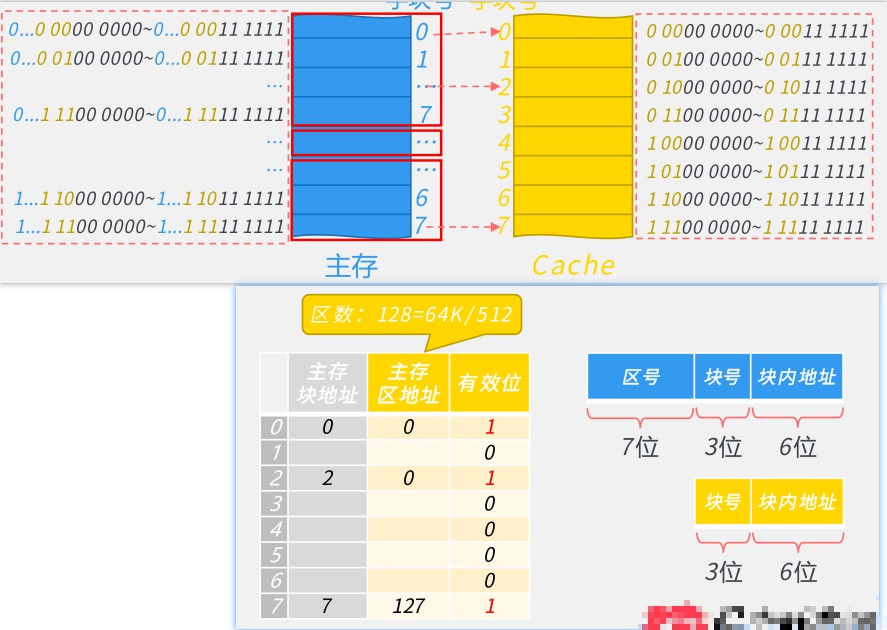

# 3.3.2 直接映像

- 主存分区,对号入座

- 主存字块只能映像到Cache特定的块中

- 将主存空间按Cache大小分区,则每区块数=Cache块数

- 某区某块只能存入Cache的相同块号中

- 优点:数据访问时,只需检查区号是否相等即可

- 缺点:替换操作频繁,命中率比较低

# 3.3.3 组相连映像

- 先分区再分组,组内随意放

- 将主存空间按Cache大小分区,则每区块数=Cache块数

- 主存每区和Cache按同样大小划分成组,则每区组数=Cache组数

- 某区某组某块只能存入Cache的相同组号中,组内随意

- 组间直接映像,组内全相连映像

- 优点:块冲突概率低,块利用率大幅提高,块失效率降低

- 缺点:实现难度和造价要比直接映像方式高